一致性测量

通过使用图4(http://happytesting.spaces.eepw.com.cn/articles/article/item/99613)列出的各种测试码型,可以方便地进行发射机测试。每种码型都是为与评估码型的测试有关的特点选择的。CP0 (D0.0加扰序列)用来测量确定性(Dj)抖动,如数据相关抖动(DDJ); CP1 (没有加扰的D10.2全速率时钟码型)不会产生DDJ,因此更适合评估随机抖动(Rj)。

抖动和眼高在应用均衡器功能及相应的时钟恢复设置(二阶PLL、10 MHz的闭环带宽及0.707的阻尼系数)后使用100万个连续单位间隔测得。抖动结果计算得出,其超越实测的数据样本总量,迅速提取1 x 10-12 BER水平时的具体抖动性能。例如,在抖动推断中,把实测Rj (rms)乘以14.069,可以计算得出目标Rj。

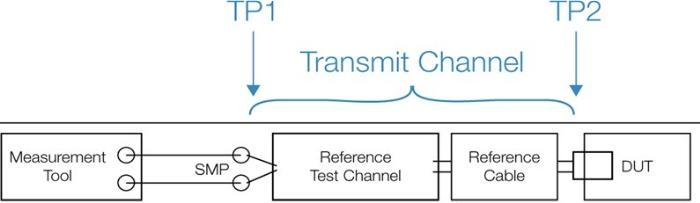

图6. 发射机测试点。

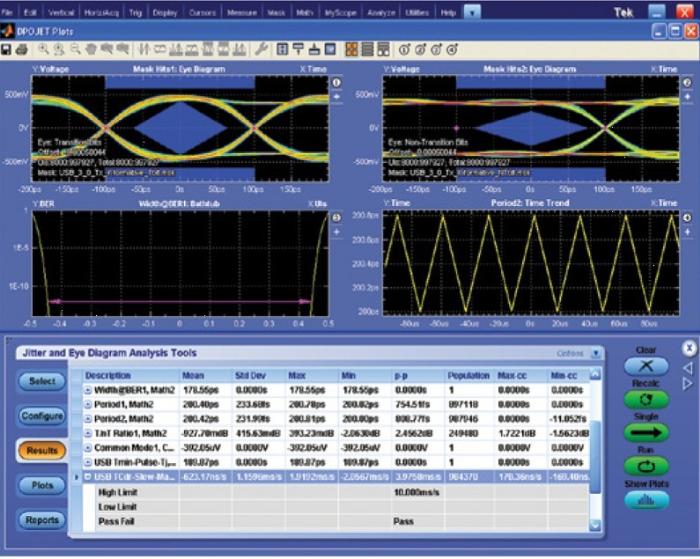

图7. DPO/DSA70000系列选项USB-TX,用于USB 3.0标准化的测量及信息性的测量。

图8. 使用DPOJET调试USB 3.0,包括自定义控制设置。

图6显示了标准化的发射机一致性测试设置,包括参考测试通道和电缆。测试点2 (TP2)距被测器件(DUT)最近,测试点1 (TP1)则是远端的测量点。注意,所有发射机标准化的测量都在TP1的信号上执行。

在TP1采集信号之后,数据使用称为SigTest的软件工具处理,这与官方PCI Express一致性测试类似。对要求预一致性测试、检定或调试的应用,可以使用其它工具,进一步了解变化条件或参数下的设计特点。带有选项USB-TX的泰克MSO/DPO/DSA70000系列示波器可以执行所有USB 3.0标准化和信息性物理层发射机测试,如图7所示。单键自动软件工具,如USB-TX,通过保证正确配置测试设备,节约了时间。实验室技术人员就可以准确地运行测试,而不是非得要深入了解USB规范的高级工程师。在测试结束后,详细的测试通过/失败报告将列出可能发生设计问题的地方。如果不同测试地点(如公司实验室、测试机构、等等)得到的结果相互矛盾,可以使用以前运行的测试中保存的数据运行测试。

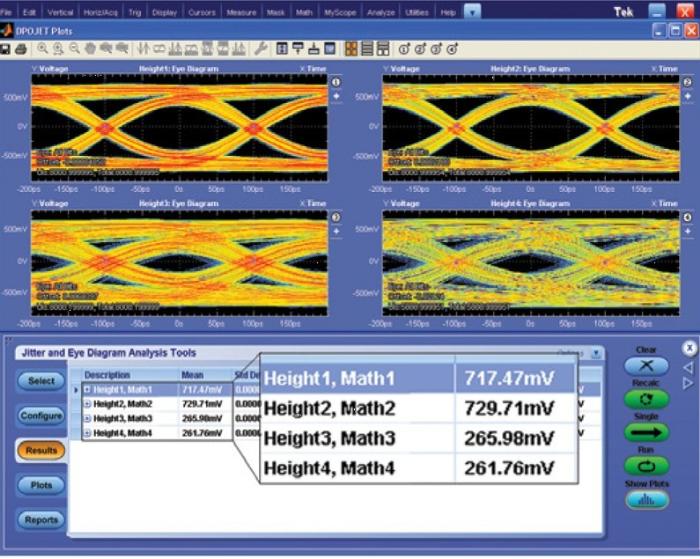

带有选项USB-TX的TekExpress自动测试软件利用基于DPOJET通用分析功能的检定和调试环境。灵活的抖动和眼图分析软件包可以更多地以用户自定义方式控制分析参数,帮助加快调试过程,大大简化设计检定。例如,可以一次显示多个眼图,用户可以分析不同时钟恢复技术或软件通道模型的影响。另外,可以运用不同的滤波器,分析SSC解决系统互操作能力的效果。

图9. 带有12英寸和24英寸轨迹的ISI电路板。

图10.12英寸和24英寸PCB轨迹的幅度和相位响应。

参考测试通道

可以通过两种方法捕获TP1的“远端”信号。第一种方法使用USB-IF基于硬件的电缆和夹具,在TP1处采集数据。第二种方法使用从TDR、VNA或仿真器中提取的模型,在软件中仿真硬件通道效应。公认的通道模型是一个S参数文件,其中包括幅度和相位响应影响。先在TP2处或距发射机最近的地方采集信号,然后使用S参数文件对采集的数据求卷积,这个S参数文件已经被转换成一个有限脉冲响应(FIR)滤波器(如需更多地了解泰克示波器上的滤波器应用,请参阅www.tektronix.com上的白皮书“任意FIR滤波器的原理、设计和应用”)。

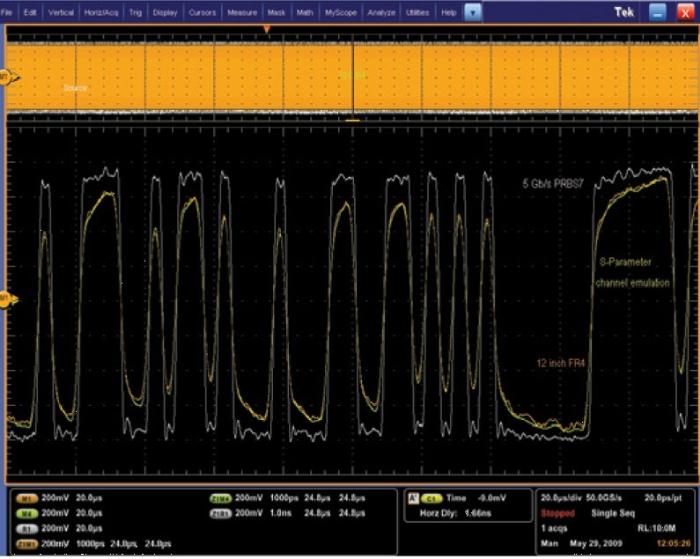

通过这种方法,工程师可以使用变化而又重复的具体通道要求测量被测器件。例如,我们比较一下不同PCB轨迹长度中的5 Gb/s信号测量结果。图9显示了连接到12英寸和24英寸轨迹的ISI测试电路板,图10提供了相应的Sdd21通道响应。

图12.24英寸轨迹的硬件通道仿真和软件仿真。

图13.12英寸、24英寸轨迹后的5 Gb/s眼图,硬件仿真通道(左)和软件仿真通道(右)。

在包括硬件通道时、在没有包括硬件通道时都要采集测试信号。图11和图12显示了每个轨迹长度的原始信号(白色)、远端硬件响应(橙色)和使用S参数数据卷积后的原始信号。图13包括来自基于硬件和基于软件的测试数据的眼图。

均衡

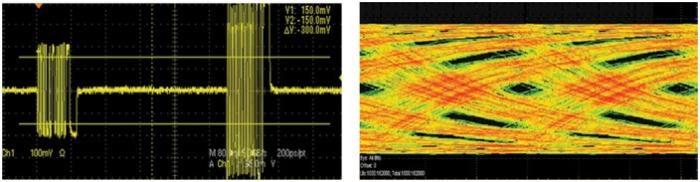

由于明显的通道衰减,SuperSpeed USB要求某种形式的补偿,使接收机上的眼图张开。为实现这一点,发射机上使用均衡功能(采取去加重形式)。规定的标称去加重比是3.5 dB,采用线性标度时为1.5x。例如,在跳变比特电平是150 mV pk-pk时,非跳变位电平将是100 mV pk-pk。

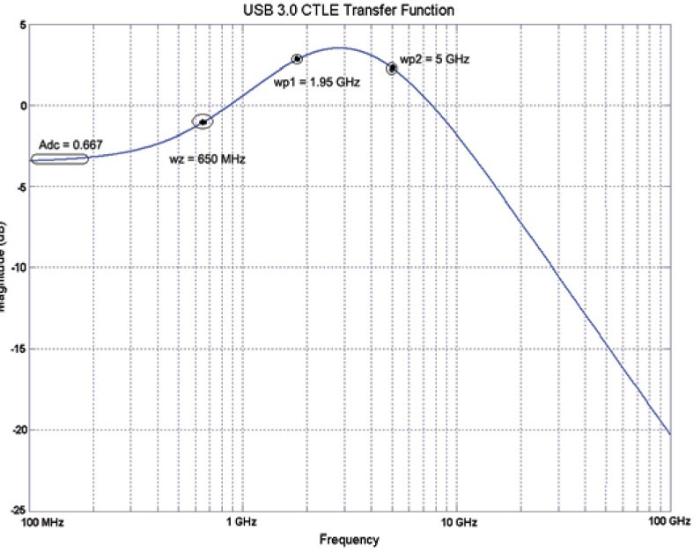

一致性均衡模型是连续时间线性均衡器(CTLE)。CTLE实现方案包括片上滤波器、有源接收机均衡滤波器或无源高频滤波器,如电缆均衡器中的滤波器。这个模型特别适合一致性测试,因为它可以简单地描述转函。CTLE在频域中使用一套电极和零极实现,得到所需频率上的峰值。如前所述,带有选项USB-TX的TekExpress软件包括参考一致性通道以及要求的CTLE滤波器,这些都组合到一个文件中。

图14. USB 3.0 CTLE转函和幅度响应。

除使用TekExpress自动软件中提供的一致性滤波器外,设计人员可以使用泰克串行数据链路分析(SDLA)软件,验证不同的CTLE参数及其对链路性能的影响。CTLE实现方案的优势在于,与其它方案相比,其设计起来更简单,能耗更低。但在某些情况下,由于适应性、精度和噪声放大方面的限制,它们可能不够。其它技术包括前馈(FFE)均衡和判定反馈(DFE)均衡,这种技术采用使用标度因数加权的数据样点,补偿通道损耗。CTLE和FFE都是线性均衡器,因此,都会发生信噪比劣化,表现为高频噪声提高。但是,DFE采用反馈环路中的非线性成分,因此使噪声放大达到最小,并补偿ISI。图16显示了明显通道衰减后的5 Gb/s信号,以及使用去加重、CTLE和DFE技术均衡后的信号。

检定和调试

在整个设计检验和一致性测试过程中,总是需要调试工具,解决信号完整性或抖动问题。由于电路余量下降增加了复杂性及链路问题,芯片设计人员和系统集成商需要拥有智能统计分析功能的工具以及可视化工具,如直方图、抖动频谱和BER“浴缸”曲线。DPOJET分析图,如频谱图和趋势图,可以提供深入信息,而不是简单地显示测量数据和结果。趋势分析显示定时参数怎样随时时间变化,如频率漂移、PLL启动瞬态信号或电路对电源变化的响应。抖动频谱分析可以显示抖动和调制源(相邻振荡器和时钟)的精确频率和幅度、电源噪声或信号串扰。

在测试失败后,非常重要的一点是能够使用自动测试软件,从“一致性模式”切换到“用户自定义的”抖动和眼图分析工具系列。通过DPOJET软件,用户可以控制时钟恢复、滤波、参考电平、Rj/Dj分离技术或测量限制和选通等参数。除规定的标准化USB 3.0测量及信息性USB 3.0测量外,它还包括许多定时测量、幅度测量和眼图测量。

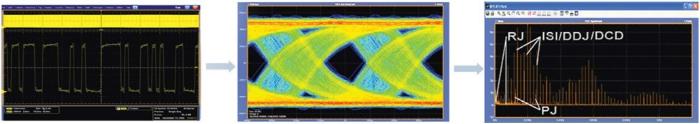

图17显示了调试和分析抖动的一个程序实例。首先,我们使用相对较大的数据样本总量采集数据,进行抖动分析,包括SSC的影响。一个33 kHz的SSC周期要求30 us的时间窗口。一旦采集了数据,眼图分析可以迅速以可视化方式指明电压和定时性能。这个眼图显示周期抖动和数据相关抖动过高。最后,我们执行抖动分解,隔离信号完整性问题。抖动频谱图突出显示抖动成分及对应的相对幅度和频率。

图18. USB 2.0和3.0接收机测试实例。

想了解更多测试测量最新资讯?想与测试测量专家互动?敬请关注泰克科技官方微博:http://weibo.com/tekchina

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。