此外,这一技术在支持长距离、实施成本和最终用户成本方面也面临重大挑战。通过比较,串行总线只发送一个比特流并具有“自时钟”机制,因此数据和时钟之间没有时序偏差(即同时传输的比特到达时间之差)。借助串行传输,消除了信号同步问题,而且整体性能更强。

然而,随着技术进步,这个性能障碍得到解决,另一个问题又出现在人们面前。速度更快的新技术在化解此项挑战的同时,也使设计更趋复杂,而且持续变化的标准也产生了更多新的设计难题,这会妨碍产品快速上市并增加开发成本。包括 PCI-Express、XAUI、RapidIO、USB, HDMI 和 SATA 在内的一些新的串行数据总线架构所带来的数据处理量比几年前要大好几个数量级。

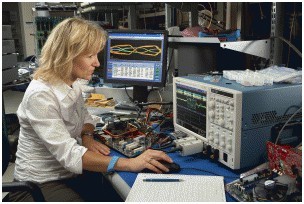

为了确保产品开发的所有阶段之间的交互操作性,标准化势在必行。领先的技术公司已经将2.5-Gbit/s 和 3-Gbit/s的设计产品化,而5-Gbit/s 技术也即将面世,同时,10Gbs 已经用于网络通信的设计。在如此复杂多变的环境下,工程师极需一些测试解决方案,帮助其迅速轻松地发现和纠正设计中的问题。在此,泰克提供了完备的串行数据测试解决方案,有助于工程师开发产品,并能够确保符合最新的串行数据测试要求。

在设计过程中,工程师需要确认高速串行总线能够正确传送数据,同时串行传输问题也不会给其他系统元件带来不利影响。最新标准具有更快的边缘速率和更窄的数据脉冲,对验证、调试和测试过程提出了一些独特且严格的要求。

随着数千兆数据传输率在数字系统中屡见不鲜,信号完整性(即集成电路正确运行所具备的信号质量)也逐渐成为设计人员关注的重点。数据流中一个比特的错误都会对指令或数据交换处理的结果产生巨大的影响。

可能会对传输信号质量造成损害的因素包括:

千兆信号速度:超高速传输率、低电压差分信号和多级信号传输更容易引起信号完整性问题、差分时滞、噪音和模拟干扰的问题。由于串行总线可以为单通道架构,也可以为多通道架构以提升数据量,此时将造成整体设计更复杂并可能引起通道时滞定时干扰问题。

抖动:由于较高的数据速率和嵌入的时钟的影响,现代串行设备会很容易受到抖动的影响,抖动会产生传输错误并导致比特差错率,性能下降。抖动通常使信号偏离理想的时间。抖动通常源自串扰、系统噪音、同步开关输出和一些其他的常见干扰信号。

传输线影响:传输线作为电源和信号传输的中介,可以是简单的无源线路元件,如电线、电缆和芯片印刷电路板(PCB)互连。借助串行数据技术,信号发送器、传输线和接收器共同构成了串行数据网络。而由此带来的传输效应(如反射和阻抗不连续)会严重影响信号质量并导致传输错误。

噪音:噪音是在采样数据中出现的任何多余的信号。噪音来自外源(如 AC 电源线)和内源(如数字时钟、微处理器和开关电源)。噪音可能是瞬时的,或者是宽带随机噪音,但都会引起抖动和信号完整性问题。

带有嵌入式时钟的高速数字信号具有越来越像模拟系统的特征,使设计验证和系统集成面临更严峻的挑战。由于信号即使在很小的失真或抖动下都可能使系统变得不稳定,这令用户在各种条件下实施精确验证、特征描述和强度测试都要面临新的问题。

高速串行数据测试过程

受消费需求的推动,设计工程师经常需要将新功能集成到采用领先技术的系统设计中。为了便于工程师使用,每种串行数据技术的设计和操作都会在唯一的标准文档中进行定义,该文档通常由行业委员会编写。每个标准还必需经过专业测量和一致性测试过程,这就给现有复杂的设计任务又增加了新的工作。这些标准针对高速数据信号传输和编码、封装、时钟嵌入、传输属性和一致性测试过程。设计人员根据明确的高速串行技术标准和测试程序,方能够创造出具有良好互操作性的产品。

典型的高速串行数据测试过程包括:

通常工程师需要全面评估芯片和系统性能。在千兆赫速度下,抖动、发射器和接收器之间的阻抗不连续,或者硬件和软件之间的系统级干扰都会引起定时问题。每个设计阶段都需要全方位的分析工具进行更深入的观察,进而全面描述特征并发现隔离边缘设计或系统影响。

领先的设计、缩短产品开发周期、扩展供应链和符合特定技术标准都必需要通过优秀的验证和测试工具实现。借助先进的数据分析能力,泰克的测试和测量仪器是用户在开发过程早期发现设计问题,缩短串行数据产品的设计周期,加快进入市场的时间以及降低成本的有效手段。敬请关注下一篇博文:主要的高速串行接口技术及测试解决方案

想了解更多测试测量最新资讯?想与测试测量专家互动?敬请关注泰克科技官方微博:http://weibo.com/tekchina

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。