作者:Chris Loberg

泰克高级技术市场经理

随着JEDEC最近发布LPDDR3和DDR4规范,转向下一代内存技术的趋势在加速。首先是LPDDR3,它将在移动设备和超薄笔记本电脑中代替LPDDR2,并将于2014年开始商业部署。然后出现的是新的同步DDR4规范,也就是下一代DRAM,用于从笔记本电脑到服务器的一切产品中,其可能会在2015年早期开始在生产中部署。

新内存规范的发展趋势是可以预测的:速度更高、密度更高、封装更小、能耗下降。对负责电气验证和调试的设计工程师来说,新标准带来了大量的显著变化和新的测量挑战。更快的速度和更低的电压相结合,意味着信号完整性比以前更加重要,同时更密集的封装将带来信号接入挑战。

本文阐述了这些新标准给电气验证带来的变化,描述了怎样为正确接入LPDDR3和DDR4内存系统信号做好准备。本文还将考察仪器选型及在这些新兴标准上执行电气检验测试所需的技术。

LPDDR3概述

2012年5月,JEDEC出版了《JESD209-3低功率内存器件标准》。与LPDDR2相比,LPDDR3提供了更高的数据速率、更高的带宽和能效、更高的内存密度。LPDDR3实现了1600 MT/s的数据速率,采用大量的新技术,包括写置平和命令/地址训练、可选的片上端接(ODT)及低I/O电容。

与LPDDR2一样,LPDDR3支持综合封装和各种离散封装类型,满足各种移动设备的要求,并允许设计人员选择最能满足其产品需求的选项。LPDDR3保持了LPDDR2的高能效功能及信令接口,支持快速时钟停止/启动、低能耗自行刷新及智能阵列管理。

从电气验证角度看,LPDDR3正通过结合实现更低的工作电压和更高的带宽,来挑战系统功率极限。相比之下,第一代LPDDR的工作电压为1.8 V,频率为200 MHz。LPDDR2的电压下降到1.2V,同时速度提高到533 MHz。现在,LPDDR3同样要求1.2V,但工作频率是800 MHz。这意味着信号完整性将成为重要因素,以在更短的1.25 ns时钟周期上验证时钟周期。表1显示了两代技术的比较结果,表明需要更高带宽的示波器,以保持信号完整性。

表1 –LPDDR3中更快的速度要求更高的示波器带宽。

|

|

LPDDR2 |

LPDDR3 |

|

最大SE转换速率(V/ns) |

3.5 |

4 |

|

典型时钟速率(MHz) |

400 |

800 |

|

周期(ns) |

2.5 |

1.25 |

|

上升时间,10% - 90% (ps) |

738 |

369 |

|

典型信号摆幅(V) |

.08 |

.08 |

|

最小上升时间(ps) |

229 |

200 |

DDR4概述

DDR4规范于2012年9月发布,与DDR3相比,要求更高的性能、明显提高的封装密度、改善的可靠性及更低的能耗。如表2所示,电压从1.5V下跌到1.2V,降低了能耗,而性能因数几乎翻了一倍,达到3,200 MT/s (每秒百万次传送)。其它变化包括更高的密度、以支持内存密集型服务器应用,更高的数据速率,能够堆叠引脚、放置更高密度的模块。

表2 – 与DDR3,DDR4规范要求更快的传送速度、更高的密度及更低的能耗。

|

特点 |

DDR3 |

DDR4 |

备注 |

|

信令变化 |

|||

|

电压(内核和I/O) |

1.5V |

1.2V |

降低能耗 |

|

低压标准 |

是 (DDR3L@ 1.35V) |

预计 (DDR4L, 可能1.05V) |

内存能耗下降 |

|

数据速率(MT/s) |

800, 1066, 1333, 1600, 1866, 2133 |

1600, 1867, 2133, 2400, 2667, 3200 |

演进到更高速度 |

|

密度 |

512Mb – 8Gb |

2Gb – 16Gb |

满足更高容量的内存需求 |

|

读/写时延 |

AL+CL |

AL+CL |

扩大值 |

|

DQ驱动器(ALT) |

40欧姆 |

48欧姆 |

为点到点应用优化 |

|

DQ总线 |

SSTL 15 |

POD 12 |

降低I/O噪声和能耗 |

|

RTT值 |

120, 60, 40, 20 |

240, 120, 80, 60, 48, 40, 34 |

支持更高的数据速率 |

|

堆叠引脚 |

否 |

是 |

适用于未来的更高密度的模块 |

从测试角度看,与LPDDRR3一样,转向更高的传送速度和更低的电压将提高验证内存技术时对信号完整性和定时及余量测量的重视程度。为适应提高的测量复杂性,JEDEC对要求的测试方法作了大量的变化及更新。

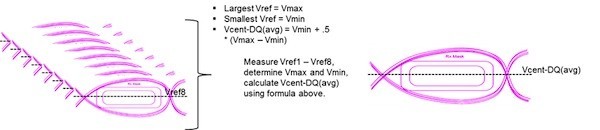

最重大的变化之一是建议要求确定参考电压或V center,以使用可变方法执行一致性测试。对DDR3来说,这个值固定在750 mV。新方法涉及多次采集输出数据(DQ)及一个数据选通信号(DQS) Write突发。然后测量每个信号的最大到最小电压值,使用简单的公式建立一个平均值。然后这将成为DQ参考电压,用来使用眼图确定中心及进行参考测量。图1说明了这一过程。

图1 – 早期DDR4验证建议指明了一种可变方法,来建立参考电压或V center。

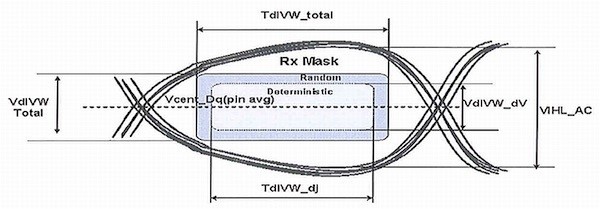

图2 – 草议的DDR4规范增加了眼图要求。

在许多串行标准的引导下,DDR4现在对高于2133的速度采用统计抖动测量方法。对低于2133的速度,所有抖动被假设为确定性抖动(DJ)。对2133及以上速率,测试将同时考察DJ和随机性抖动(RJ)。到目前为止,许多抖动定时参数还没有公布,但设计人员应知道将要求进行抖动测试。扩大DDR4中抖动测试的一个优势是,如果被测器件未能满足抖动要求,那么测试测量厂商界将提供强健的抖动分解工具,可以帮助隔离问题根源。

此外,与DDR2和DDR3一样,JEDEC不再要求根据信号转换速率降低建立时间和保持时间测量的通过/失败极限额定值。在与工程师们讨论这个问题时,JEDEC标准委员会发现,复杂的额定值下降程序很难被理解,也很少被执行。一般来说,大多数工程师依赖进行标准转换速率测量。在DDR4中,这已经被上面介绍的Vref平均和眼图模板测量所代替。

示波器带宽

尽管与LPDDR3、特别是DDR4有关的大量细节还有待最终确定,但顶级性能特点足以使设计人员面向电气检验测试做好准备。第一个问题一般是:“我的示波器需要多少带宽?”对DDR测试应用,示波器是评估读/写特点、突发行为及生成眼图的主要工具。

如表3所示,可以使用最大转换速率导出带宽要求,JEDEC为特定技术规定了最大转换速率,来确定上升时间和等效边沿带宽。推荐的实际示波器带宽基于特定应用及最终用户可以容忍的差错率。例如,在DDR4中,推荐在芯片组开发或内存控制器检定中使用16 GHz带宽示波器,而对嵌入式系统或低成本调试应用中的部件验证,12.5 GHz就足够了。

值得一提的是,如果这些建议只基于时钟速率,那么为DDR4推荐的示波器带宽将只有4 GHz。对更多带宽的需求源于内存中的转换速率要明显快于类似串行标准中的转换速率。

表3 – 这里是根据预计应用测试各代DDR推荐的示波器带宽。

|

代 |

DDR |

DDR2 |

DDR2 |

DDR3 |

DDR3 |

LPDDR3 |

DDR4 |

|

速度 |

所有速率 |

最高400MT/s |

最高800MT/s |

最高1600MT/s |

最高2400MT/s |

最高1600MT/s |

最高3200MT/s |

|

根据JEDEC最大转换速率 |

5 |

5 |

5 |

10 |

12 |

8 |

18 |

|

典型电压摆幅 |

1.8 |

1.25 |

1.25 |

1 |

1 |

0.6 |

0.8 |

|

20-80上升时间(ps) |

216 |

150 |

150 |

60 |

50 |

45 |

27 |

|

等效边沿带宽 |

1.9 |

2.7 |

2.7 |

6.7 |

8.0 |

8.9 |

15.0 |

|

推荐带宽(根据最终用户任务,与提供的示波器带宽配套) |

|||||||

|

芯片组开发/信号完整性 |

2.5 |

3.5 |

4.0 |

12.5 |

12.5 |

12.5 |

16 |

|

系统级测试 |

2.5 |

2.5 |

3.5 |

8 |

12.5 |

12.5 |

12.5 |

|

调试(低成本) |

2.0 |

2.0 |

2.5 |

6 |

8 |

8 |

12.5 |

信号访问

图3 – 内存插补器可以使探头接入拥有优秀保真度的测试信号。

[图示内容:]

Solder-In Probe Tip: 焊接探头尖端

Memory Chip: 内存芯片

Memory Component Interposer: 内存器件插补器

Retention Socket with guide posts: 固定插座,带有导柱

Board under test: 被测电路板

图4 – 泰克DPO70000系列示波器上运行的示波器滤波器提供了带和不带插补器电路效应的视图。

尽管可能也能使用手持式探头,但在多个探头尖端和测试点之间同时保持良好的电接触会很难。例如,某些JEDEC测量要求三个或三个以上的测试点,外加其它信号,如片选、RAS和CAS,在判定内存状态时可能会需要这些信号,到目前为止,插补器上的焊接探头连接是最好的方法。

随着测试复杂程度不断增长,三模探头可以成为节约时间的利器。这种功能允许探头在+和-之间以差分方式测量,或在信号和接地之间以单端方式测量。通过在探头尖端有效启用三个焊接连接,设计人员可以使用探头上的控制按钮或示波器上的菜单命令,在差分模式和单端模式之间切换,而不会扰动内存器件。

把探头的+连接焊接到单端数据或地址线,把探头的–连接焊接到相邻的线上,这种技术可以说明怎样把其用于内存应用中。然后,可以使用一只探头,并在两个单端测量模式之间切换探头,来测量这两个信号。这把LPDDR3和DDR4上的探测密度有效地提高了一倍,减少了对焊接和重新焊接连接的需求。

捕获信号

一旦已经探测了信号线,下一步是评估特定列或行,或隔离特定数据码型,分析信号完整性问题,如数据相关抖动、定时或噪声问题。DDR4测量现在已经扩展到包括眼图。

可以使用多种方式,识别和隔离读突发和写突发或其它总线条件。最简单的方法之一,是使用DQS或数据选通信号,识别读突发或写突发开头。例如,DQS一直在写开始时为高,或在读开始时为低。示波器的硬件触发功能可以触发突发的这个前置码部分,保证只在采集的波形开始的地方捕获读或写。由于它们基于硬件,硬件窗口触发快速准确地反映实际定时性能。它们能够采集特定DQ位,并使用示波器上的余辉设置查看眼图性能。还可以使用硬件触发,评估三态突发条件定时。

对比较通用的DQS突发捕获功能,图5所示的可视触发使得设计人员能够把定制设计的形状直接“放在”示波器显示画面上,其中形状边界为被采集的DQS或数据选通定义触发事件。可以在示波器格线上移动、旋转或修改这些形状,并可以与传统示波器触发功能相结合,全面准确地捕获信号。通过使用形状,可视触发为在复杂的多列DDR4环境中准确地测量目标列提供了强大的工具。

图5 – 可视触发消除了来自其它输入列的多条眼图轨迹,为在目标列上进行准确的DDR4测量提供了强大的工具。

图6 – DPO70000显示画面顶部的三角形说明怎样使用波形搜索和标记功能,识别一定时间间隔内的所有DDR写突发。

JEDEC验证测量

即使在比较复杂的下一代技术出现之前,JEDEC检验测试也一直很难使用通用工具实现。每种内存技术的JEDEC规范都规定了一系列一致性测量,如抖动、建立时间和保持时间、瞬态电压、信号过冲和下冲、转换速率及其它电气质量测试。

由于JEDEC指定的测量方法、参考电平、通过/失败极限等本身固有的复杂性,为LPDDR3和DDR4检验测试提供专用测量工具至关重要。使用此类工具可以保证正确配置测量,消除仅使用通用工具时要求的几小时的手动仪器设置时间。

DDR分析软件自动实现DDR器件测试的设置和测量过程。其提供的测量满足JEDEC规范,通常允许设计人员在非标准设备或系统实现方案上为测量任务定制设置。由于DDR4中增加了抖动测量,整合抖动和眼图分析软件可以在器件或系统一致性测试失败时帮助追踪问题的根本原因。

一个新出现的要求是需要在低能耗DDR系统通常使用的高球数系统中同时查看系统特点,而这种需求在LPDDR3中只会提高。这样的视图有助于确定信号完整性问题的根源,在多通道、多列环境中执行验证。如图7所示,其中一个解决方案是把逻辑分析仪设置成采集大量的输入通道,如本例中的四个34通道行。然后通过逻辑分析仪上的复用器解析通道,传送到示波器。这可以同时查看所有信号和信号类型,包括地址总线、DQ或选通,而不需重复探测。

图7 – A 逻辑分析仪可以与示波器结合使用,查看LPDDR3高球数系统的特点。

小结

下一代内存标准拥有更高的数据速率及降低的能耗。对需要验证、测试和调试设计的系统设计人员,更快的速度和更低的电压相结合,使这些工作变得日益棘手。此外,由于增加了为DDR4规划的抖动和眼图评估方法,测试正变得更加复杂。

幸运的是,测试测量行业正在利用各种工具迎接挑战,如插补器、探测解决方案、DDR检验测试软件和高性能示波器,设计人员需要利用这些工具,来检验和调试最新的内存设计和标准。

想了解更多测试测量最新资讯?想与测试测量专家互动?敬请关注泰克科技官方微博:http://weibo.com/tekchina

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。